高速数字电路PCB设计中的阻抗控制

发布日期:2021-07-06

随着半导体工艺的飞速发展,IC器件集成度和工作时钟频率不断提高。以往在一块比较复杂的PCB上的高速网线只有几根或几十根,现在则是在一块PCB上只有几根或几十根网线不是高速信号线;以往认为数字电路设计只要把握逻辑正确,物理连线似乎只要连接上就能使电路正常工作;而现在越来越多的电子产品设计体现出高速、高性能、高密度和高复杂度的特点,尤其在通讯、计算机、航空航天以及图象处理等领域。系统的主频越来越高,更加严重的挑战来自半导体工艺技术的进步,日渐精细的工艺技术使得晶体管尺寸越来越小,因而器件的信号跳变沿也就越来越快,从而导致更加严重的高速数字电路系统设计领域的信号完整性问题:传输线效应(反射、时延、振铃、及信号的过冲与欠冲)、信号问串扰等。为此,电子系统设计师必须从传统的设计方法向现代的电子系统设计方法转变,这既是形势需要,也是发展的必然趋势。

1 高速数字电路概念

1.1 什么是高速数字电路

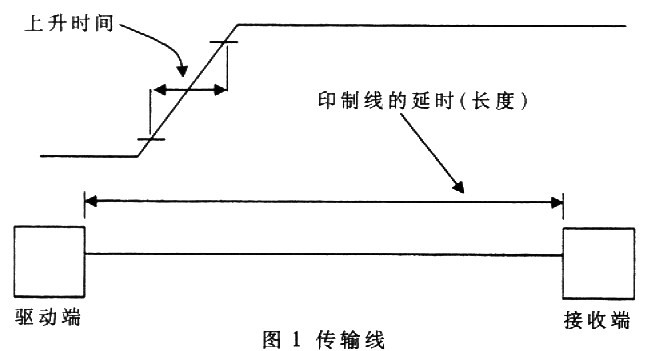

PCB上的高速电路设计,主要是以器件和连接器件的印制线为主要分析对象的。以往在器件的时钟频率不是很高、时钟的上升或下降沿变化不是很陡的情形下,可以用集总参数的形式来表示印制线,而当器件的时钟频率变得很高时(比如:超过50MHz),时钟的上升或下降沿很小时(一般地在1ns~5ns之间),这时就不能将印制线用集总参数来表示,必须引入分布参数来表示印制线特性,这就是传输线的概念(图1)。关于传输线的分析是高速PCB设计当中最基本也是最核心的部分,下面简要介绍传输线的定义和高速电路设计相关的一些概念。

1.2 PCB的板层材料和板层结构

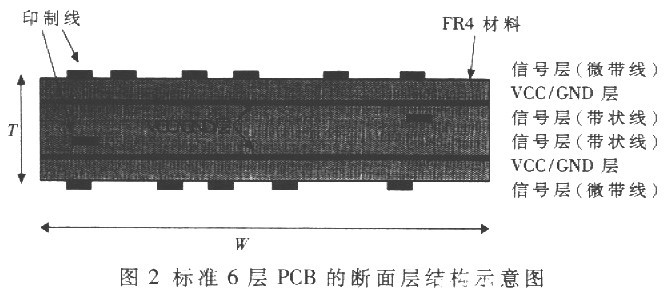

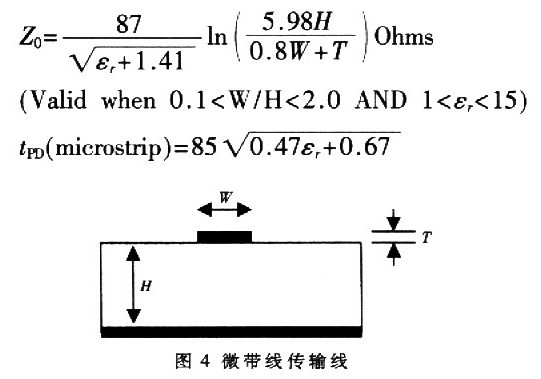

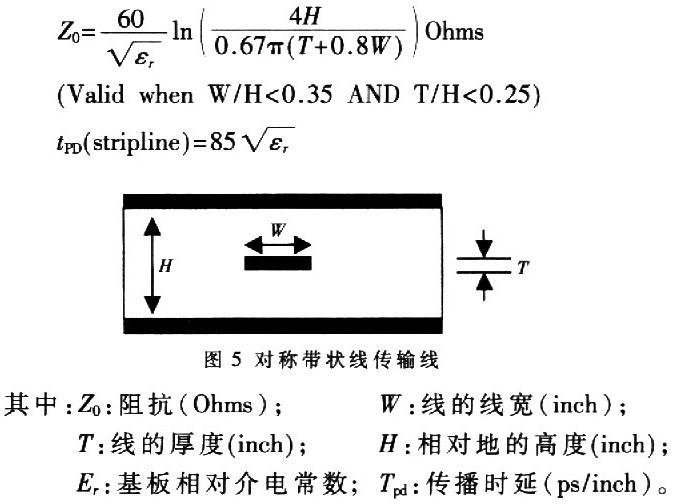

图2所示是一个标准6层PCB的断面层结构示意图,其它多层PCB的层设置与此相似。在PCB上的印制线所形成的传输线基本上有两种形式,即微带线(Microstrip)和带状线(Stripline)。带状线又分为对称性带状线和非对称性带状线。在上面的示意图中,顶层和底层形成微带线传输线 (图4),中间的3、4层形成带状传输线(图5)。

2 PCB上的高速电路传输线阻抗计算及阻抗控制

2.1 传输线的等效模型

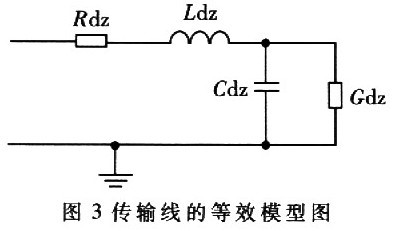

PCB板上的传输线可等效为图3所示的串联和并联的电容、电阻和电感结构(RLGC模型)。串联电阻的典型值0.25-O.550hms/foot,因为 绝缘层的缘故,并联电阻阻值通常很高。将寄生电阻、电容和电感加到实际的PCB传输线中之后,传输线上的最终阻抗称为特征阻抗ZO。线径越宽,距电源/地 越近,或隔离层的介电常数越高,特征阻抗就越小。

图3所示即长度为dz的传输线的等效模型,根据此模型推导出的传输线的特征阻抗为:

L:每单位长度传输线上的电感;

C:每单位长度传输线上的电容。

2.2 PCB上的传输线的阻抗和延时计算公式

根据图4得出微带线的阻抗及单位长度延时计算公式:

根据图5得出对称带状线的阻抗及单位长度延时计算公式:

2.3 传输线的阻抗控制布线规则

从上面的分析可知,阻抗和信号的单位延时与信号的频率没有任何关系,它们只是与PCB的板层结构、材料的相对介电常数、走线的物理特性(线宽与线的厚度)有关。这些结论对于认识高速PcB和进行高速PcB设计尤其重要。其次信号传输线在外层的传输比在内层的传输快,所以在安排关键网线的布线时,要将这些因素考虑在内。

从前面高速电路的特性分析可以得出,阻抗控制是实现良好的信号传输的重要前提。而从PCB的层结构和传输线的阻抗计算公式可见,同样的一根阿线,当线宽和走线的特性不改变时,其线的阻抗值只取决于PCB的材料、层结构特性。这样,当同一根网线走在不同的PCB层面上时,其阻抗值将发生改变。而这在高速电路设计当中是不允许的。

我们设计了一个密度非常大的高速PCB板,板上绝大部分信号都有阻抗要求。如CPCI信号线要求65ohms,差分信号要求1000hms阻抗,其他信号均按500hms。而从PCB走线空间要求考虑,必须至少要lO层信号走线。最终确定为一个16层PCB的设计方案。

因为该板总厚度不能超过2mm,所以叠层设计有一定的难度。而且还要考虑几个叠层的问题:

l.每个信号层都要有参考平面相邻,能保证其阻抗和信号质量;

2.每个电源层都要有完整的地平面相邻,使得电源的性能得以较好的保证;

3.层的堆叠要求平衡,避免出现板翘曲。

介质的介电常数取4.3计算。通过上述叠层方案的设计,为了保证信号阻抗的要求,对于线宽和线间距的设置按计算结果设定。

其中线宽:

1)表层信号走线为5Mils,阻抗为58.70hm;

2)表层CPCI信号走线为4.5Mils,阻抗为61.70hm;

3)内层信号走线为4.5Mils,阻抗为50.20hin;

4)表层和内层BGA出线区域的走线为4mils。表层阻抗64.60hm,内层阻抗52.70hm;

5)表层微带差分走线,线宽5Mils,线间距为6Mils,阻抗为100.540hms;

6)内层带状差分走线,线宽4.5Mils,线间距为lOMils,阻抗为96.60hms。

其中线间距定于如下:

1)表层5mils信号的线间距为5mils(低速信号);

2)表层4.5mils CPCI信号线间距为9mils;

3)内层4.5mils信号线间距为7mils;

4)表层和内层BGA出线区域的走线的线间距为4mils(尽可能少用);

5)内层差分信号之间以及与其它信号线之间的间距保持至少25mils;

6)表层差分信号线之间以及与其它信号线之间的间距保持至少20mils。

该板加工后。用POLAR-Cits500阻抗测试仪测试其附连板,500hms的阻抗线实测范围在47.52-52.330hms,600hms的阻抗线实测范围在57.65~61.350hms,1000hms差分阻抗实测范围在93.65~106.350hms,表明在设计和加工中阻抗值严格控制在 500hms±5%,600hms±5%,l0Oohms±10%范围内的。

3 PCB上的LVDS差分信号及其阻抗控制

3.1 LVDS差分信号

LVDS(Low Voltage Differential Signal)低压差分信号,最早由美国国家半导体公司提出的一种高速串行信号传输电平,由于它传输速度快,功耗低,抗干扰能力强,传输距离远,易于匹配等优点,迅速得到诸多芯片制造厂商和应用商的青睐,并通过TIA/EIA的确认成为该组织的标准(ANSI/TIA/EIA-644 standard)。LVDS信号被广泛应用于计算机、通信以及消费电子领域。

3.2 LVDS差分线的阻抗设计

LVDS信号的电压摆幅只有350MV,为电流驱动的差分信号方式工作,最长的传输距离可以达到10米以上。为了确保信号在传输线当中传播时,不受反射信号的影响,LVDS信号要求传输线阻抗受控,其中单线阻抗为500hms,差分阻抗1000hms。在实际应用当中,利用一些高速电路仿真分析工具,通过合理的设置层叠厚度和介质参数,调整走线的线宽和线间距,计算出单线和差分线阻抗结果,来达到阻抗控制的目的。

但是在很多时候,同时满足单线阻抗和差分阻抗是比较困难的。一方面,线宽W和线间距S的调整范围会受到物理设计空问的限制,例如在BGA或直插型边缘连接器内的布线和线宽受焊盘尺寸和间距的限制;另一方面,W和S的改变都会影响到单线和差分阻抗的结果。目前利用一些专用的高速PCB设计分析软件或 POLAR公司的阻抗计算软件可以很方便地计算出达到预定阻抗值的线宽和线间距关系。

3. 3 LVDS差分信号布线规则

一般来说,按照阻抗设计规则进行差分信号布线,就可以确保LVDS信号质量。在实际布线当中,LVDS差分信号布线应遵循以下几点:

1.差分对应该尽可能地短、走直线、减少布线中的过孔数,差分对内的信号线间距必须保持一致;避免差分对布线太长,出现太多的拐弯。采用45度拐弯,不能使用90°拐弯。

2.差分对与差分对之间应该保证10倍以上的差分对间距,减少线间串扰。必要时,在差分对之间放置隔离用的接地过孔。

3.LVDS差分信号,信号不可以跨平面分割。尽管两根差分信号互为回流路径,跨分割不会割断信号的回流,但是跨分割部分的传输线会因为缺少参考平面而导致阻抗的不连续。

4.尽量避免使用层间差分信号。在PCB板的实际加工过程中,由于层叠之间的层压对准精度大大低于同层蚀刻精度,以及层压过程中的介质流失,层间差分信号不能保证差分线之间间距等于介质厚度,因此会造成层间差分对的差分阻抗变化。因此建议尽量使用同层内的差分。

5.在阻抗设计时,尽量设计成紧耦台方式(即差分对线间距小于或等于线宽)。

6.设置合适的PCB层叠结构,确保其他电平信号与LVDS信号的隔离。可能的话将高速的TTL/CMOS等信号与LVDS布线在不同的信号层上,并且用电源和地层隔离开来。

7.差分信号对布线的长度应该保持一致。

在高速数字电路:PCB设计中阻抗控制技术是极其重要的,在PCB设计中必须采用各种行之有效的方法,以确保高速PCB设计的成功实现。

在正常的PCB设计条件下,主要以下几个因素由PCB制造对阻抗产生影响:

1、介质层厚度与阻抗值成正比。

2、介电常数与阻抗值成反比。

3、铜箔厚度与阻抗值成反比。

4、线宽与阻抗值成反比。

5、油墨厚度与阻抗值成反比。

精鸿益电路是一家专业从事各类高精密电路板打样与批量制造的线路板厂家,提供单面线路板、双面线路板、高精密多层线路板的加工制作服务,欢迎询价。